Digital Twin Technology for Panel Assemblies

Using digital twins for panel design, simulation, and lifecycle management.

Digital Twin Technology for Panel Assemblies

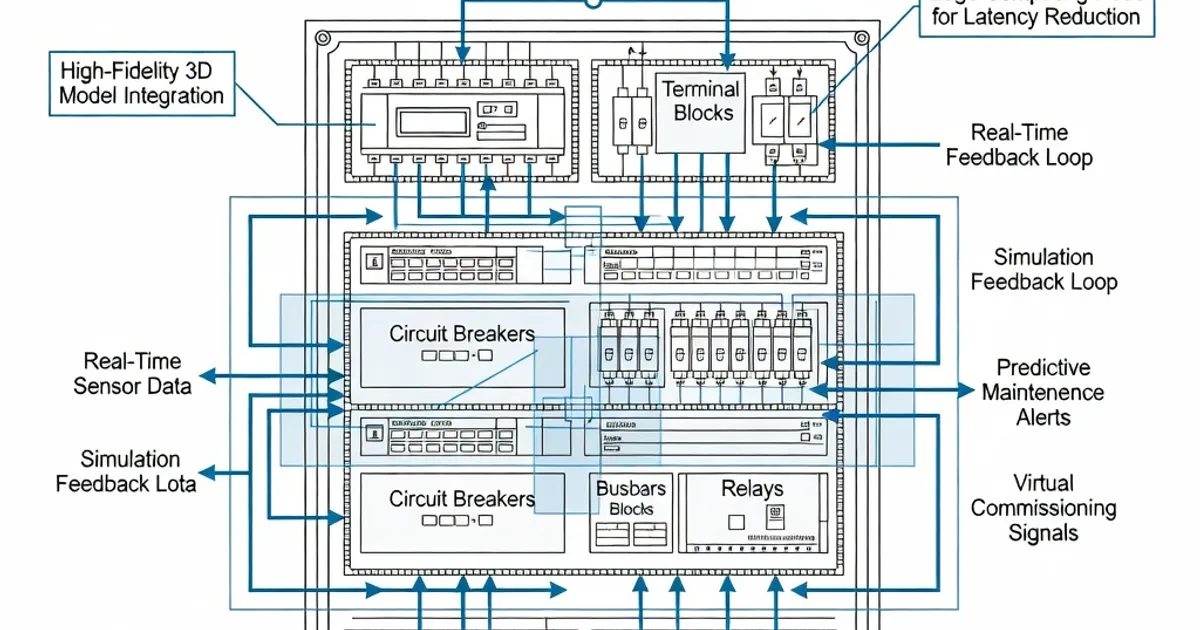

Digital twin technology transforms the design, verification, and lifecycle management of low-voltage panel assemblies built to IEC 61439. By creating validated, physics-based virtual replicas of assemblies, engineers can perform thermal, electrical, mechanical, and environmental simulations that support the verification routes defined by IEC 61439‑1:2020 — testing, comparison to tested assemblies, or assessment by calculation and analysis. This article explains how digital twins integrate with IEC 61439 requirements, summarizes key technical facts with clause references, compares verification routes, describes modeling best practices, and lists vendor examples and implementation guidance for low-voltage panels and motor control centers.

Overview: Why Digital Twins Matter for IEC 61439 Panel Assemblies

IEC 61439 shifts emphasis from exhaustive type-testing toward design verification and calculated assessment when equivalent evidence exists. Digital twins supply that evidence by modelling steady-state and transient behaviors (temperature rise, short-circuit electromechanical forces, voltage withstand, harmonics and DC effects), by checking clearances/creepage, and by documenting traceable data for lifecycle changes. Per IEC 61439‑1:2020 the standard allows verification by testing, by comparison with a tested reference, or by assessment — a path that digital twin outputs can satisfy when validated against test data or product standards [5][2].

How Digital Twins Map to IEC 61439 Verification Methods

- Testing (Type Tests): Physical tests remain mandatory when calculated or comparative methods cannot demonstrate compliance. Digital twins complement testing by focusing tests on critical items and by reproducing test setups virtually to reduce iterations [5].

- Comparison to Tested Assemblies: Digital twins document equivalence of functional units, dimensions, busbar layouts, and power losses relative to a tested reference assembly. IEC 61439 requires that the “same basic design” principle be demonstrable when using comparison [5][3].

- Assessment by Calculation (Design Verification): Validated numerical models (thermal, electromagnetic, structural) can be used to verify temperature rise, short‑circuit withstand, clearances, and IP classification where permitted by the standard. Models must use realistic boundary conditions: rated diversity factor (RDF), ambient ≤35 °C unless otherwise specified, and correct cable/busbar losses per product standards (e.g., IEC 60890 for certain thermal calculations) [1][3][5].

Key Technical Facts, Parameters and IEC Clause References

Below are principal technical parameters that digital twins must address, along with the relevant IEC 61439 clauses and specific modeling considerations.

- Temperature Rise Verification — Digital models compute temperature rise for busbars and conductors using rated currents, RDF and power losses. IEC 61439‑1:2020 Section 10.10 focuses on temperature verification for loaded circuits; digital verification is appropriate up to 1,600 A in multi-compartment assemblies if models are validated and conservative assumptions applied. For some calculation methods and for assemblies up to 630 A, IEC 60890 methods are the established thermal calculation reference and are commonly integrated into digital tools [5][3].

- Short‑Circuit Withstand (Electrical and Mechanical) — Models must predict electrodynamic forces, peak let‑through current and energy, and the mechanical strength of mounting/fastening. IEC 61439‑1 Clause 10.11 requires verification of short‑circuit withstand and the mechanical strength of materials and joints; digital twin finite‑element or multi‑physics simulations can be used where validated against tests or product standard data [5][1].

- Clearances and Creepage Distances — Virtual checking of phase‑to‑phase separations, phase‑to‑earth distances and creepage is required for dielectric withstand. IEC 61439‑1 Clause 10.3 defines constructional requirements; digital twins model geometry and pollution degree to verify the required clearances (for example typical phase‑to‑phase clearances of the order of ≥8 mm depend on rated voltage and pollution degree) [2][5].

- Degree of Protection (IP) and Shock Protection — Enclosure performance (IP ratings) and internal protection arrangements (Class I/II shock protection) are covered in Clauses 10.4 and 10.5. Digital twins can model ingress scenarios, sealing performance, and internal accessibility to verify compliance with IP and shock protection criteria when supported by validated enclosure thermal/flow models and component ingress test data [5].

- DC Systems, Power Converters and Harmonics — IEC 61439‑1:2020 explicitly acknowledges DC and converter equipment within assemblies. Digital twins must therefore model DC steady-state heating, harmonic losses in conductors and transformers, and converter switching effects. Such modeling typically requires time-series simulation and frequency-domain harmonics analysis, validated with product datasheets and converter manufacturer tests [5][4].

- Lifecycle and Environmental Durability — Digital twins support accelerated lifecycle prediction (e.g., 30‑year performance) under environmental loads such as humidity, pollution, and temperature cycling. These predictions use material aging models, corrosion data, and cumulative thermal stress analyses to inform maintenance intervals and spare‑parts provisioning, aligned with IEC 61439 durability expectations [2].

Comparison Table: Verification Routes and Digital Twin Role

| Verification Route | What It Verifies | Where a Digital Twin Helps | Limitations / When Physical Tests Required |

|---|---|---|---|

| Type Testing (physical) | Temperature rise, short‑circuit, dielectric, IP, endurance | Pre‑test virtual validation, reduce iterations, reproduce test conditions | Mandatory when novel design, high currents >1,600 A without validated model, or components lack tested product data [5] |

| Comparison with Tested Assembly | Equivalence of functional units, dimensions, busbar losses | Automate and document equivalence checks; extract metrics for direct comparison | Requires demonstrable sameness of key geometry, functional unit, and losses; not applicable if components differ significantly [5][3] |

| Assessment by Calculation (Digital Twin) | Thermal, electrical, mechanical, dielectric performance | Primary verification method where permitted; simulation of harmonics, RDF, DC effects; lifecycle forecasts | Must be validated against test data or product standard curves; some extreme conditions still require tests [1][3] |

Modeling Specifics: Temperature, Short‑Circuit, Clearances, IP and DC

Digital twin fidelity matters. The following technical modeling recommendations align with IEC clauses and industry guidance:

- Temperature modeling — Use conductor/busbar loss data at operating temperature, include contact resistances (connectors, bolted joints), model RDF and load diversity across circuits, and set ambient at ≤35 °C for standard verification unless the application specifies otherwise. For assemblies up to 630 A, integrate IEC 60890 algorithms where appropriate; for assemblies up to 1,600 A multi‑compartment calculations can be accepted if validated and conservative assumptions are applied [3][5].

- Short‑circuit simulation — Simulate peak and asymmetrical currents, electrodynamic forces, and the thermal and mechanical impulse on supports and busbars. Ensure conductive path lengths of non‑protected conductors do not exceed 3 m unless specifically justified — this is a practical rule adopted in design practice and referenced in IEC‑related guidance [3].

- Clearance/creepage checks — Convert CAD geometry into dielectric check routines that account for pollution degree, overvoltages and impulse withstand levels; verify against IEC 61439‑1 Clause 10.3 and the appropriate voltage‑dependent tables [2][5].

- IP and shock protection — Use CFD and enclosure sealing models to validate ingress protection levels, and carry out accessibility checks to demonstrate compliance with Class I/II shock protection per Clauses 10.4 and 10.5 [5].

- DC and converters — Include steady‑state DC heating (I²R) and switching losses, and superimpose harmonic content from converters on conductor/transformer heating models. Validate converter thermal models against manufacturer test data; IEC 61439‑1:2020 expansions for DC highlight the need for explicit verification when DC equipment is integrated [5][4].

Tools, Vendor Examples and Industry Practices

Many industrial CAD/CAE platforms and vendor ecosystems already integrate digital twin workflows aligned to IEC 61439 verification demands:

- Rockwell Automation advertises the FLEXLINE 3500 MCC with digital twin capabilities that support design, simulation and manufacturing traceability consistent with IEC 61439‑1/2 practice for motor control centers [7].

- Siemens, ABB, Schneider Electric, Eaton and Rittal provide toolchains (NX/Simcenter, ABB Ability, EcoStruxure, EPLAN integrations, Rittal enclosure data) enabling thermal and mechanical simulation of assemblies. While vendors publish differing levels of twin‑specific documentation, their product workbooks and application notes document the calculation and comparison routes of IEC 61439 [3][2][4].

- Manufacturer workbooks (for example ABB’s “The Standard IEC 61439 in Practice”) give practical calculation examples and rules for conductor arrangements, contact resistances and busbar sizing; such resources are essential for validating digital twin assumptions [3].

Practical Implementation Workflow

Adopt a structured workflow to ensure digital twin outputs are acceptable evidence for IEC 61439 verification:

- 1. Define scope and reference standards: Identify the IEC 61439 parts applicable (61439‑1 general rules, 61439‑2 for switchgear, and other part numbers for specific assemblies). Determine whether DC equipment or converters will be present and include relevant product standards such as IEC 60947 where switching devices are concerned [5][2][3].

- 2. Build validated component models: Import manufacturer data for ACBs, busbars, contactors, converters and cables. Where vendor loss curves and mechanical test results exist, use them to parameterize models; otherwise plan targeted physical tests for validation [3][7].

- 3. Run multiphysics simulations: Execute steady‑state thermal runs (with RDF scenarios), transient thermal runs for fault heating, electromagnetic simulations for short‑circuit forces, and CFD for enclosure temperature distribution and IP ingress scenarios [1][5].

- 4. Compare or calibrate against tested references: If relying on comparison, document sameness of functional units, geometry and losses. If relying on calculation, validate model outputs against tested assemblies or publish product curves. Capture margins and conservative assumptions in a verification report [5][3].

- 5. Produce certified verification dossiers: Compile simulation reports, model inputs, versions, and justification of boundary conditions into a dossier to satisfy IEC verification records and for future lifecycle changes. Include traceability to component data sheets and software versions.

Best Practices and Known Limitations

- Best Practices

- Align all thermal verifications to 35 °C ambient unless the application specifies otherwise and include RDF in load profiles [3].

- Keep non‑protected conductor lengths ideally below 3 m or justify with specific simulations/assessments [3].

- Use conservative contact resistance and connection loss assumptions unless validated by measurement [3].

- Document software tool versions, solver settings, mesh convergence results and validation datasets to ensure legal defensibility of simulation‑based verification [5].

- Limitations

- Digital twins are only as reliable as their input data and validation. For novel configurations or extremely high currents (>1,600 A) physical testing remains the safer verification route unless very strong validation exists [5].

- Vendor-specific converter and power electronics behaviors can vary; manufacturer test data should be used rather than generic models for switching losses and harmonics [4].

- Regulatory and customer acceptance: some clients or authorities may still require physical tests despite digital evidence; engage stakeholders early to agree the verification path [2].

Example Specification Table: Typical Targets and Limits

| Characteristic | Target / Typical Limit | IEC Clause / Reference | Modeling Notes |

|---|---|---|---|

| Ambient temperature for verification | ≤ 35 °C (standard) | IEC 61439‑1:2020, Section 10.10 [5] | Use for steady‑state thermal cases; higher ambients require derating |

| Temperature rise verification threshold | Calculation acceptable up to 1,600 A (multi‑compartment) with validated model | IEC 61439‑1 Section 10.10; IEC 60890 methods for certain ranges [5][3] | Apply RDF, conductor losses and contact resistances |

| Non‑protected conductor length | Prefer ≤ 3 m | Industry guidance and application practice [3] | Limit exposure and ensure mechanical protection in design |

| Clearance (phase‑to‑phase) | Typical ≥ 8 mm (depends on voltage & pollution) | IEC 61439‑1 Clause 10.3 [2] | Verify against operating and overvoltage conditions |

| IP rating verification | Simulate ingress and sealing; confirm with manufacturer test data | IEC 61439‑1 Clause 10.4; IEC 60529 for IP tests [5][1] | CFD and ingress models augment but do not fully replace standard tests |

Validation and Certification: Gaining Acceptance for Simulation Evidence

To ensure regulator, client and internal acceptance of digital twin output as verification evidence, follow these steps:

- Validate models against accredited physical tests or manufacturer test reports; document the validation matrix and deviations [3][5].

- Maintain a verification dossier including software versions

Related Panel Types

Frequently Asked Questions

Request a Quote

Tell us about your panel requirements and our engineering team will get back to you within 24 hours.

Email Us

[email protected]Call Us

+90 232 332 22 78